全国咨询热线:400-998-9522

类别:行业资讯 发布时间:2020-08-14 浏览人次:

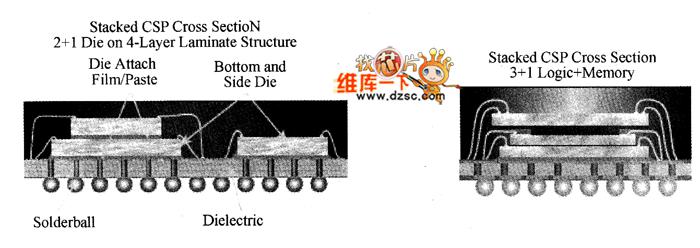

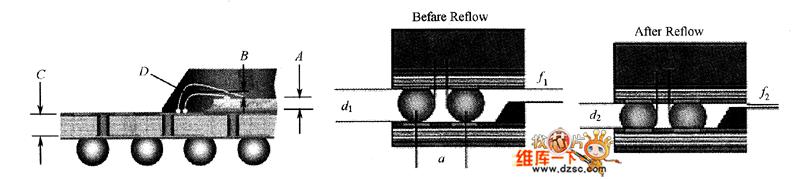

元器件堆叠封装结构...

2020-08-14东芝3D芯片堆叠策略:像建楼一样造闪存...

2020-08-13解决3D芯片堆叠难题,突破摩尔定律微缩限制...

2020-08-13中国超级激光器可撕裂真空美媒:功率等于世界总电力1万倍...

2020-08-12激光技术潜力巨大光纤激光器市场概况及国内外巨头对比分析...

2020-08-12芯片堆叠技术,或将颠覆整个半导体现有格局...

2020-08-11